时序设计基本概念介绍fanin"/>

时序设计基本概念介绍fanin"/>

时序设计基本概念介绍fanin

今天我们要介绍的概念是fanin,扇入。是指单个逻辑门的输入的数量;如下图为一个fanin为3 的与门;需要注意的是,在STA中,我们不允许出现多个输出单元同时驱动一个输入pin的情况,也就是multi-fanin的情况。这样会造成STA工具无法计算延时信息。

我们采用all_fanin来trace整个网表的扇出。但是需要注意的是all_fanin主要是时序路径上的连接,不一定完全是物理连接在一起。比如下图:

1. 往前trace 3个pin

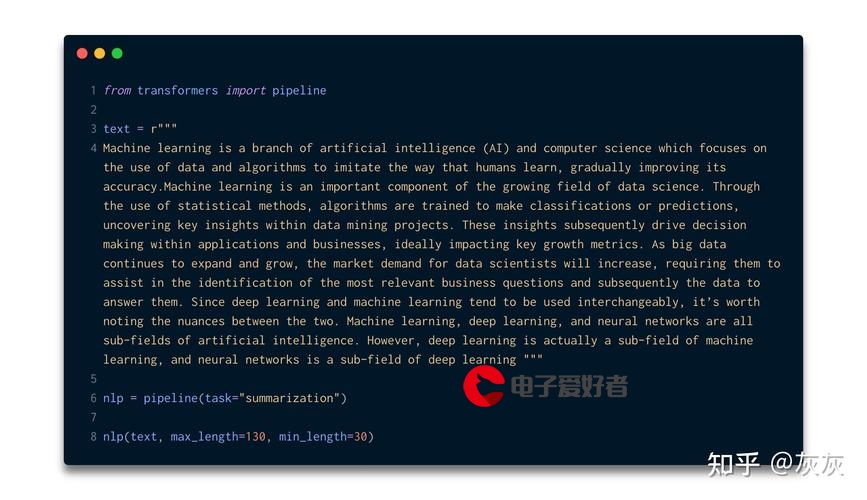

<CMD> all_fanin -to cppr_sub_2/out_float -pin_level 3

cppr_sub_2/out_float cppr_sub_2/OUTBUF2/Y cppr_sub_2/OUTBUF2/A cppr_sub_2/R2/Q

0xbe

2. 往前trace 1个cell

<CMD> all_fanin -to cppr_sub_2/out_float -level 1

cppr_sub_2/out_float cppr_sub_2/OUTBUF2/Y cppr_sub_2/OUTBUF2/A

0xc2

往期回顾

IC工程师:百万年薪路上的20个阶段,你在哪个阶段?

静态时序分析STA合集一

静态时序分析STA合集二

时序基本概念介绍<sdc合集>

数字后端基本概念合集(一)

数字后端基本概念合集(二)

数字后端基本概念合集(三)

Low Power概念介绍合集

数字后端dbGet使用方法合集

号外,数字后端交流群招人啦

IC圈的世界杯 | 论芯片设计的胜利十一人

知否?知否?Block PD应该提交哪些数据?

Timing ECO手修攻略

数字后端面试100问(2019全新版)

数字后端面试100问(校招版)

简历请戳邮箱:taozhang3260@163

觉得有用的话,给我点个好看吧

更多推荐

时序设计基本概念介绍fanin

发布评论