差异"/>

差异"/>

Q1:异步复位与同步复位差异

异步复位与同步复位

正文

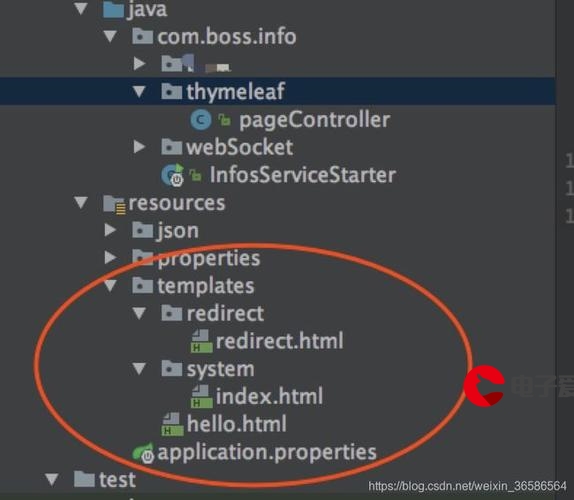

具体代码结构如下面两段代码所示。

同步复位

always@(posedge i_clk_in)

beginif(!i_rst_n)verilog codeelse verilog code

end

异步复位

always@(posedge i_clk_in or negedge i_rst_n)

beginif(!i_rst_n)verilog codeelseverilog code

end

根据上述思路,设计了一个3位计数器,展示两者之间的区别。

主要包括:

- 电路具体实现形式。

- 资源使用情况。

使用的平台是lattice的Diamond。

同步复位

//同步复位

always @(posedge i_clk_in)

beginif(!i_rst_n)r_timer_cnt <=3'd0;else if(r_timer_cnt == 3'd7)r_timer_cnt <= 3'd0;elser_timer_cnt <= r_timer_cnt + 1'b1;

end

异步复位

// 异步复位

always @(posedge i_clk_in or negedge i_rst_n)

beginif(!i_rst_n)r_timer_cnt <=3'd0;else if(r_timer_cnt == 3'd7)r_timer_cnt <= 3'd0;elser_timer_cnt <= r_timer_cnt + 1'b1;

end

结论:上述电路主要是由比较器(equal_3)、加法器(add_6)、数据选择器(mux_3)以及D触发器(wide_dffrs_r3)组成。而异步复位会比同步复位少使用一个数据选择器(mux_3)。这样在设计资源报告中可以发现少使用了一个LUT。

DATA : 2021-6-10 。Change Description : Original。

后续更新

近日拜读CrazyBingo(韩彬)所写的FPGA设计技巧与案例开发详解一书中第10章优化设计FPGA全局时钟管理模块。对于异步复位和同步复位以及系统的稳定性有了进一步的感悟。所以在本文中继续写下自己的学习感悟。

组合电路“竞争与冒险”

竞争与冒险产生的产生的原因这里就不叙述了,在组合电路中,当设计产生了竞争与冒险时,通常采用改变电路设计来破坏毛刺的产生。主要有以下几种办法:

- 采用格雷码计数器取代普通的二进制计数器。(格雷码计数器的输出只有一位跳变)

- 对于D触发器的输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害,因此应当在系统中采用同步电路。

时序电路“竞争与冒险”

时序电路也存在竞争与冒险,主要是以下两种竞争与冒险。

- clk上升沿与rst_n下降沿同时到达 (always@(posedge clk or negedge rst_n))

- clk上升沿与rst_n上升沿同时到达 (always@(posedge clk or posedge rst_n))

为了解决上述问题,最简单的同步方案的是使用主时钟对复位信号打一拍,实现信号的同步。这样解决了异步复位信号的优先级,也保证了时钟信号的同步性。

总结

我是本文的作者QImua,本文写于2021-6-10,将长期更新。

首先感谢你的阅读,由于个人能力有限,如果你有更好的想法和建议,欢迎在本文底部留言,感谢你的指正!

如果你有好的想法和建议,欢迎在本文底部留言。另外有任何疑问可以到本博客“评论专区”提出,我必知无不言,言无不尽。

DATA : 2021-6-10 。Change Description : Original。

DATA : 2021-6-12 。Change Description: Modified。

更多推荐

Q1:异步复位与同步复位差异

发布评论