分频【FPGA】"/>

分频【FPGA】"/>

晶振分频【FPGA】

所有数据对齐晶振。

6分频:【1】

module divider_six // 6分频 【0~2】

( input wire sys_clk , //系统时钟 50MHz input wire sys_rst_n , //全局复位 output reg clk_out //对系统时钟 6 分频后的信号

);reg [1:0] cnt; //用于计数的寄存器 //cnt:计数器从 0 到 2 循环计数

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0) cnt <= 2'b0;

else if(cnt == 2'd2) // 计数 到 2 cnt <= 2'b0;

else cnt <= cnt + 1'b1; //clk_out:6 分频 50%占空比输出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0) clk_out <= 1'b0;

else if(cnt == 2'd2) clk_out <= ~clk_out;

6分频:【2】

module divider_six

( input wire sys_clk , //系统时钟 50MHz input wire sys_rst_n , //全局复位 output reg clk_flag //指示系统时钟 6 分频后的脉冲标志信号

); reg [2:0] cnt; //用于计数的寄存器

//cnt:计数器从 0 到 5 循环计数

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0) cnt <= 3'b0;

else if(cnt == 3'd5) // 【5】清零cnt <= 3'b0;

else cnt <= cnt + 1'b1; //clk_flag:脉冲信号指示 6 分频

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0) clk_flag <= 1'b0;

else if(cnt == 3'd4) // 【等于4】下周期_拉高clk_flag <= 1'b1;

else clk_flag <= 1'b0;

endmodule 5分频:

从第一个晶振开始:【3+2】

2.5晶振高电平,2.5晶振低电平

clk1是 3+2

clk2是2+3

需要 clk2下降沿【拉低】clk1上升沿【拉高】

逻辑上看,可以是clk1和clk2都是高电平时,输出高电平。

clk_out = clk1 & clk2;

推荐5分频:

原因是:所有数据对齐晶振。

更多推荐

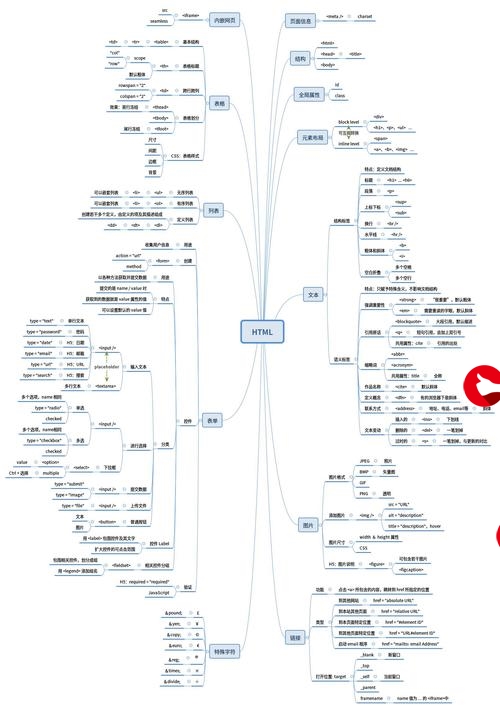

晶振分频【FPGA】

发布评论